|

Single-Chip Passive UHF RFID Tags and Readers

|

Project Goal

The goal of our team is to provide a novel design of a RFID Tag and Reader baseband system , which should be low power consumption, small size and low cost.

Project Description

In our projects, it can be divided into three main parts:

· Algorithm and Architecture design

· RTL coding

· SimuLink Co-verification

Faculty

Prof. Vincent K. N. LAU ( 劉 堅 能 )

Research Assistant

Hin Tat CHAN ( 陳 顯 達 )

Sau Wing MAN ( 文 秀 榮 )

Shunqing ZHANG ( 張 舜 卿 )

Tracking Record and Accomplishment

|

Stage |

Milestone |

Status |

|

Phase I (June 1, 2005 Aug 31, 2005) |

1) Specification study Understand the requirement Schedule Planning |

Accomplished |

|

Phase II (Sep 1, 2005 Oct 30, 2005) |

1) Algorithm design PIE Decoding Simulation Tag Architecture Design |

Accomplished |

|

Phase III (Nov 1, 2005 Jan 31, 2006) |

1) RTL coding for the Front End of Tag 2) Layout and tape-out of Tag Front End 3) Tag System Simulation in Simulink |

Accomplished Accomplished Accomplished |

|

Phase IV (Feb 1, 2006 Apr 30, 2006) |

1) RTL coding and Design for Tag 2) Tag RTL integration and Testing 3) Layout and tape-out of Tag BaseBand system |

on-going on-going on-going |

|

Phase V (May 1, 2006 Aug 31, 2006) |

1) Algorithm design of Reader RX Front End 2) Reader Architecture and Simulink Design 3) Reader RTL coding and verification 4) Reader RTL integration 5) Layout and tape-out of Reader Baseband system |

on-going on-going on-going on-going on-going |

|

Phase VI (Aug 1, 2006 Oct 30, 2006) |

|

|

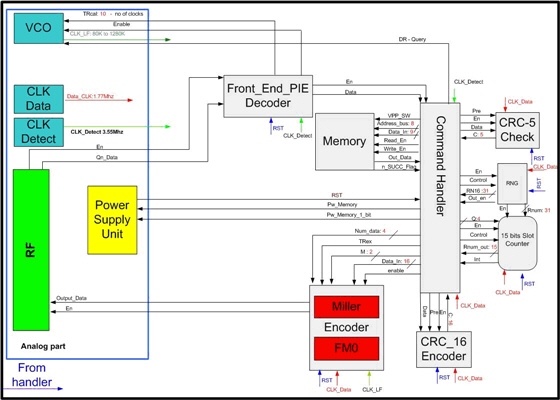

Architecture

Architecture of Tag Baseband

Layout

Layout of Tag Baseband

Die Photo