|

Single-Chip Passive UHF RFID Tags and Readers

|

Project Goal

The goal of this project is to develop, fabricate and characterize a zero-additional mask one time programmable memory devices and array in standard CMOS process.

Project Description

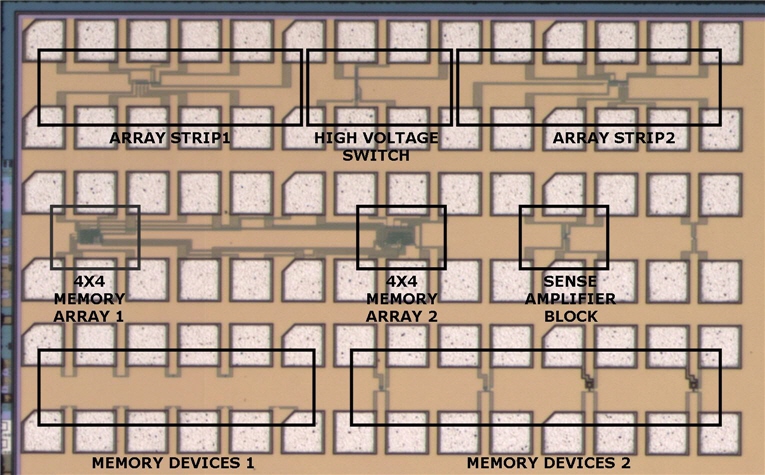

The memory device developed requires no additional mask to standard CMOS. Several OTP devices have been fabricated and characterized and evaluated in terms of RFID requirements such as low-power programming. Memory peripheral circuitries, including a high-voltage switching circuit using conventional MOS devices, have been developed to control the programming of the OTP devices.

Faculty

Prof. Mansun J. CHAN ( 陳 文 新 )

Research Assistant

Randy BARSATAN

Tracking Record and Accomplishment

|

Stage |

Milestone |

Status |

|

Phase I |

Functional Description of the memory |

Accomplished |

|

Phase II |

Device design and fabrication |

Accomplished |

|

Phase III |

Device characterization and evaluation |

Accomplished |

|

Phase III |

Circuit development – design and simulation |

Accomplished |

|

Phase IV |

Sub-array fabrication |

Accomplished |

|

Phase V |

Memory subcircuits and additional device characterization |

Ongoing |

|

Phase VI |

Memory array circuit design and tag fabrication |

|

Fabrication