|

Single-Chip Passive UHF RFID Tags and Readers

|

Project Goal

In order to achieve a low-cost solution for RFID readers, it is critical to develop a high-performance transceiver in terms of low voltage, low power, low sensitivity and wide dynamic range.

Project Description

System challenges:

The challenges in designing a single-chip RFIC transceiver for RFID readers include:

· A sensitivity as low as -90 dBm and a dynamic range as wide as 70 dB

· An output power as large as 1W (30 dBm) is required for the transmitter's power amplifier for long-distance applications.

· Strong transmitting signals from readers lie in the same frequency band as weak backscattered signals from tags.

· Since the tags will use the same modulation scheme all the time for back scattering, the received signal bandwidth varies significantly with the signal data rate.

Potential solution and research direction:

A single-chip CMOS solution not only reduces the cost but also lowers the voltage supply and the power consumption. To be compatible with both FCC and ETSI regulations, novel system architectures and circuit design techniques will need to be developed. Among the critical building blocks for the transceiver are wideband low-noise amplifier, wideband low-phase-noise frequency synthesizer, on-chip power amplifier, and wide-dynamic-range sigma delta ADC

Faculty

Prof. Howard Cam LUONG ( 梁 錦 和 )

Research Assistant

Kay Wing Chuen CHUI ( 徐 永 泉 )

Lai Kan LEUNG ( 梁 禮 勤 )

Chi Fung LOK ( 駱 智 峯 )

Shuzuo LOU ( 樓 書 作 )

Sujiang RONG ( 容 蘇 江 )

Evelyn Wenting WANG ( 王 文 婷 )

Hui ZHENG ( 鄭 慧 )

Tracking Record and Accomplishment

|

Stage |

Milestone |

Status |

|

01/05/2005 to 30/07/2005 |

1. System specifications, behavioral simulations, and building block specifications for the transceiver |

Completed |

|

01/08/2005 to 31/10/2005 |

1. Design of critical building blocks for the transceiver (synthesizer, mixer, LNA) |

Completed |

|

01/11/2005 to 31/01/2006 |

1. Submission for fabrication of critical building blocks for transceiver (synthesizer, mixer, LNA) 2. Design other building blocks for the receiver (filters, VGA, ADC) |

Completed |

|

01/02/2006 to 26/04/2006 |

1. Testing critical building blocks for transceiver (synthesizer, mixer, LNA) 2. Design other building blocks for the transceiver (DAC, PA, up-mixer) 3. Submission for fabrication of transceiver |

On-going |

|

27/04/2006 |

1. Reader transceiver testing |

|

Design

Transceiver Architecture

Frequency Synthesizer

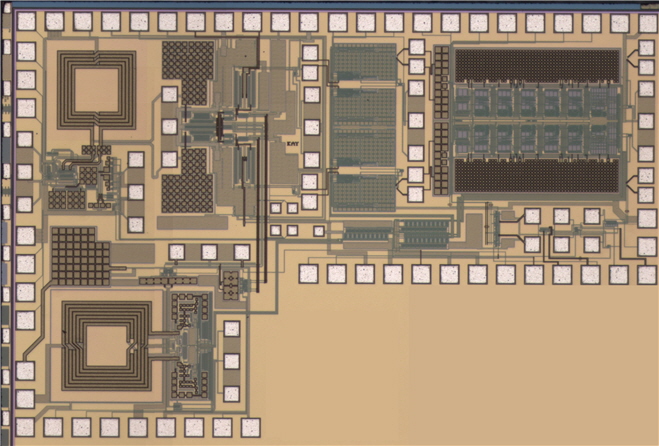

Die Photo of Frequency Synthesizer

Phase Noise Performance of Frequency Synthesizer

Receiver

Receiver Layout